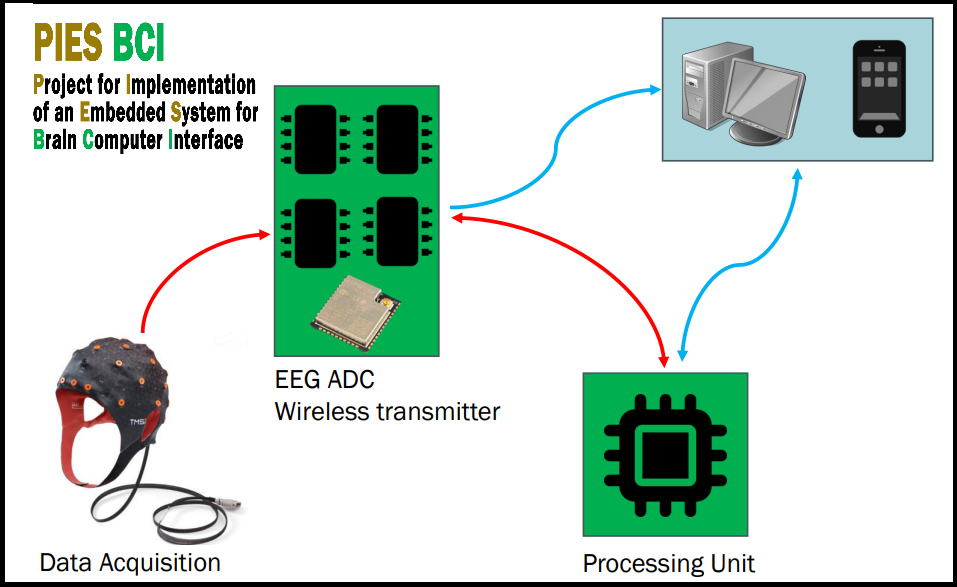

PIES-BCI: Project for Implementation of an Embedded System for Brain Computer Interface

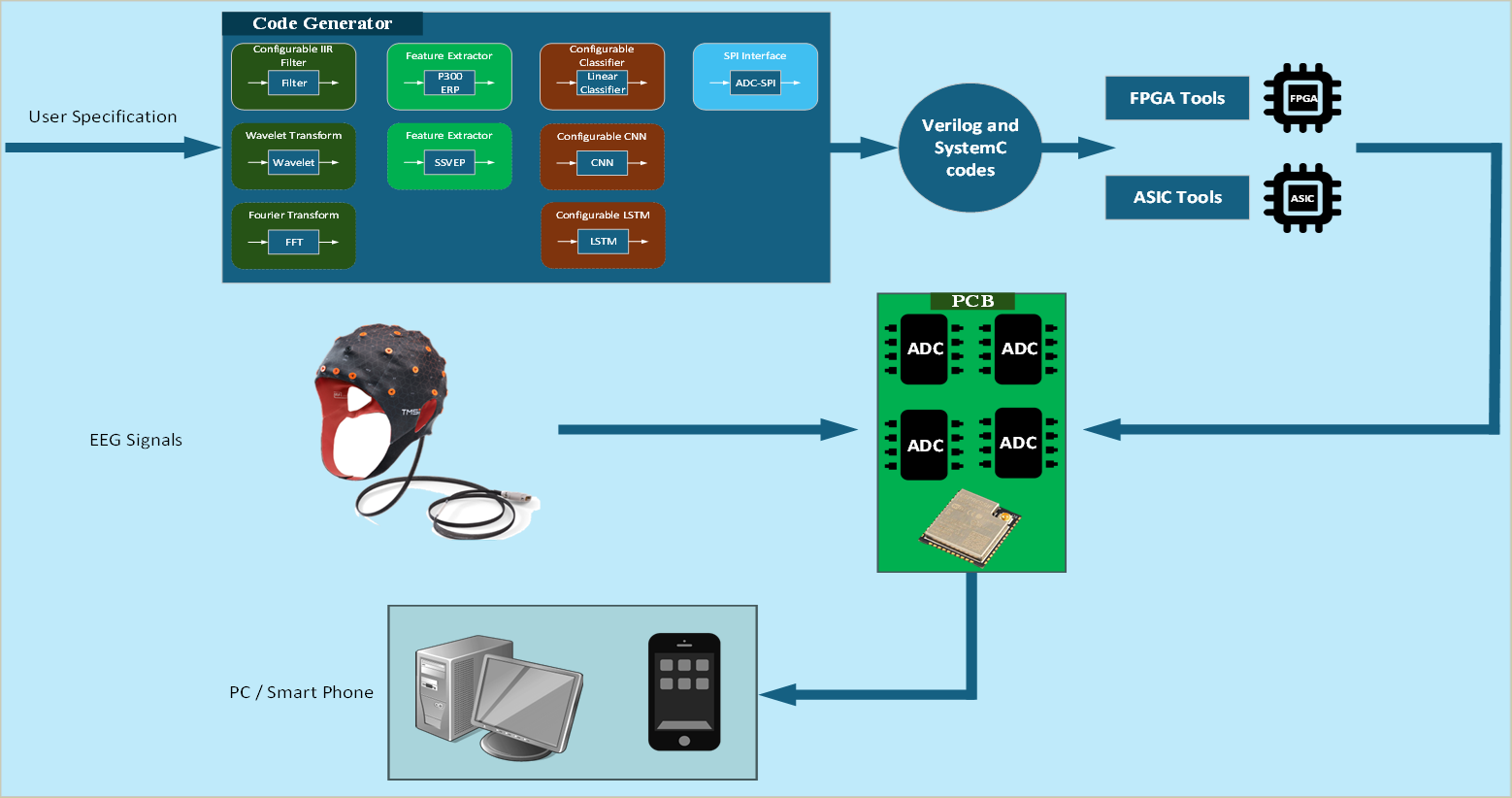

For my master’s thesis, I am designing an embedded system for a Brain-Computer Interface (BCI), specifically a P300 Speller that incorporates an IIR filter, synchronized averaging, and a linear classifier. This field presents numerous challenges, including area and power optimization, high-accuracy maintenance in DNN design, and implementing precise DSP filters. Additionally, I am focusing on the system's reconfigurability. Most chips in this area are highly customized, which can be impractical if requirements change. To address this, I am introducing degrees of reconfigurability, such as varying the number of sections in the second-order sections (SOS) IIR filter. I am also developing a high-level framework to expand my work in the future, enabling users to design their systems at a high level and then compile them for hardware implementation